CD4081 AND gates, provide the system designer with direct implementation of the AND function and supplement the existing family of CMOS gates.

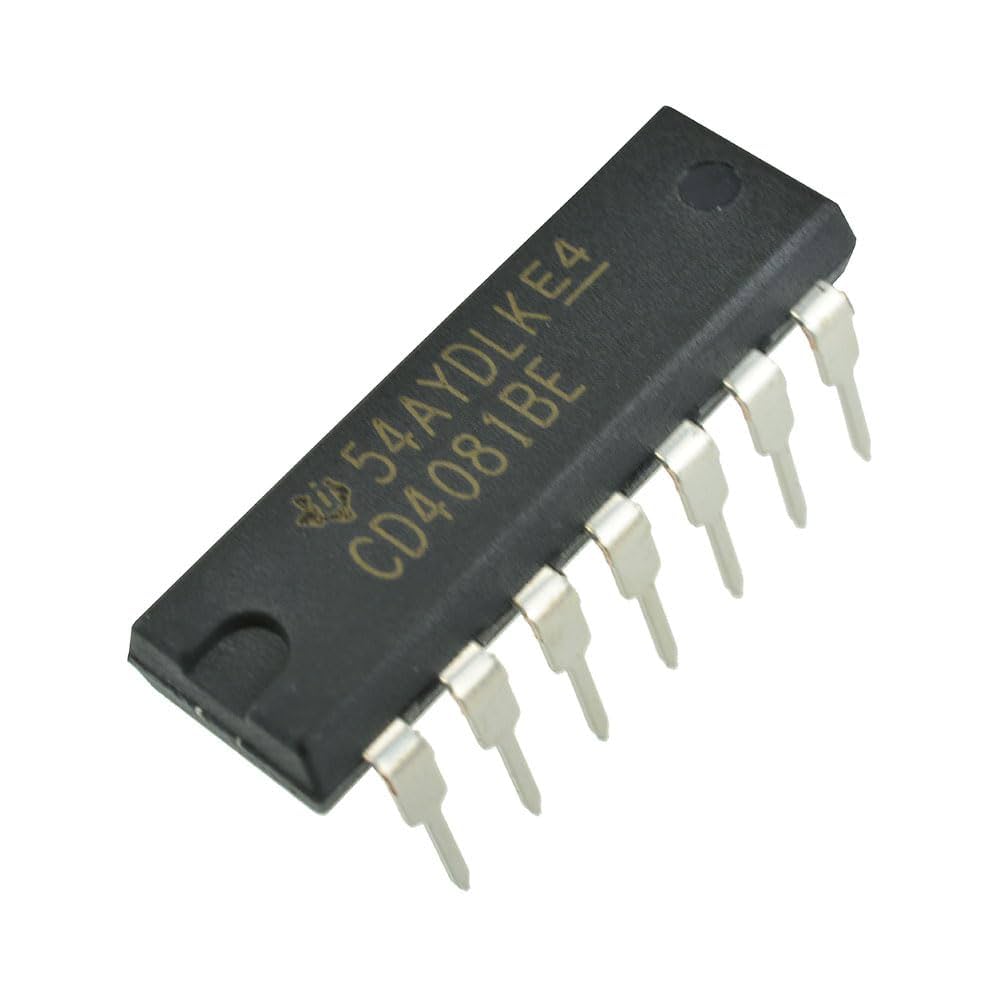

The CD4081 types are supplied in 14-lead hermetic dual-in-line ceramic packages (F3A suffix), 14-lead dual-in-line plastic packages (E suffix), 14-lead small-outline packages (M, MT, M96, and NSR suffixes), and 14-lead thin shrink small-outline packages (PW and PWR suffixes).

Features:-

- Medium-Speed Operation – tPLH, tPHL = 60 ns (typ.) at VDD = 10 V

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 µA at 18 V over full package-temperature range: 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

- 1 V at VDD = 5 V

- 2 V at VDD = 10 V

- 2.5 V at VDD = 15 V

- Standardized, symmetrical output characteristics

- 5-V, 10-V, and 15-V parametric ratings

Reviews

There are no reviews yet.